# The CDF Silicon Vertex Trigger

Bill Ashmanskas Argonne National Laboratory (for the CDF-II Collaboration) May 30, 2003

Outline

- CDF trigger overview  $\rightarrow$  focus on SVT

- How SVT works (performance)

- Why SVT works (diagnostics/flexibility)

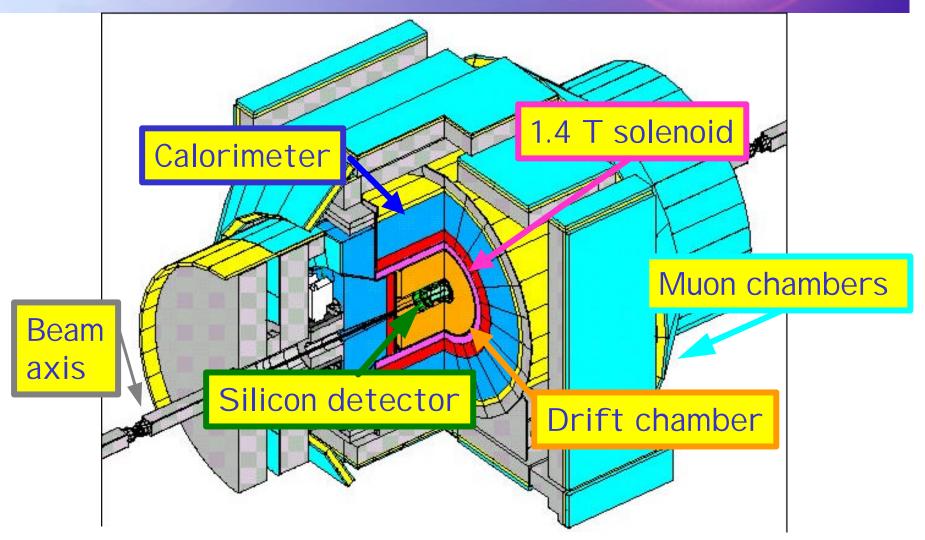

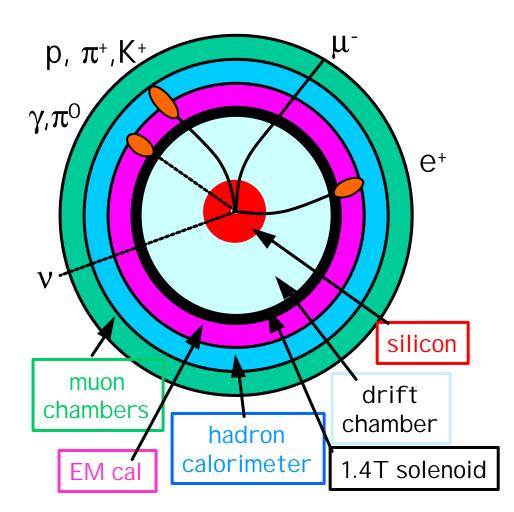

#### **CDF** Detector

- CDF: multi-purpose experiment, broad physics program

- Tevatron: E<sub>CM</sub>=1.96 TeV, T<sub>bunch</sub> = 396 (132) ns, L ~ 10<sup>32</sup> cm<sup>-2</sup>s<sup>-1</sup>

# CDF trigger (detector) signatures

Trigger exploits a wide variety of signatures ...

- e, μ from W, Z, SUSY, b

- $\gamma$ , jet,  $\nu$  (E imbalance),  $\tau$ , b jet, ...

- "Displaced" hadrons from bottom and charm decay

... to distinguish processes with a wide range of rates

- ~ 50 mb total inelastic

- ~ 100 μb bottom, charm

- 10 μb B, pT>6GeV, |y|<1</li>

- ~ 2 nb W  $\rightarrow$  ev

- ~ 5 pb top

Many trigger signatures use drift chamber tracks, e.g. coincidence of D.C. track with EM cal, muon stub, silicon hits

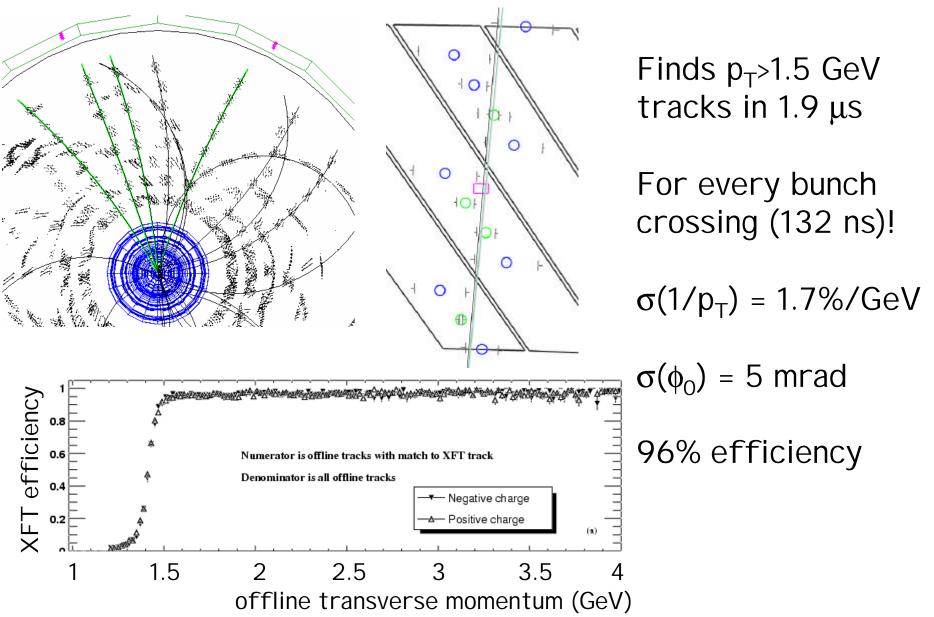

#### Level 1 drift chamber trigger (XFT)

4

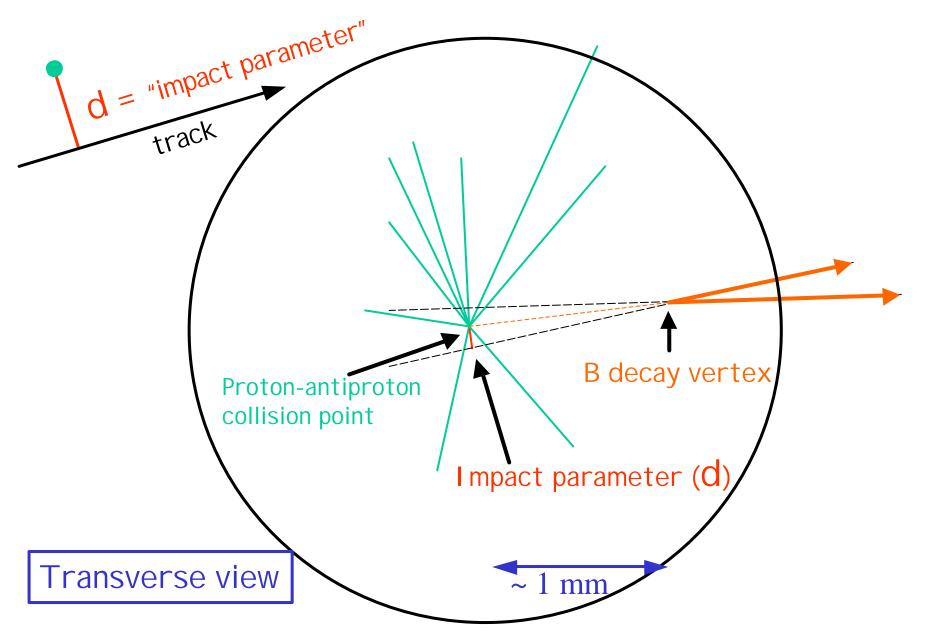

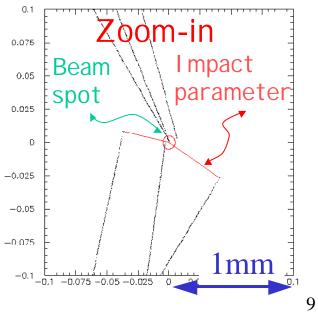

#### Exploit lifetime to select b,c decays

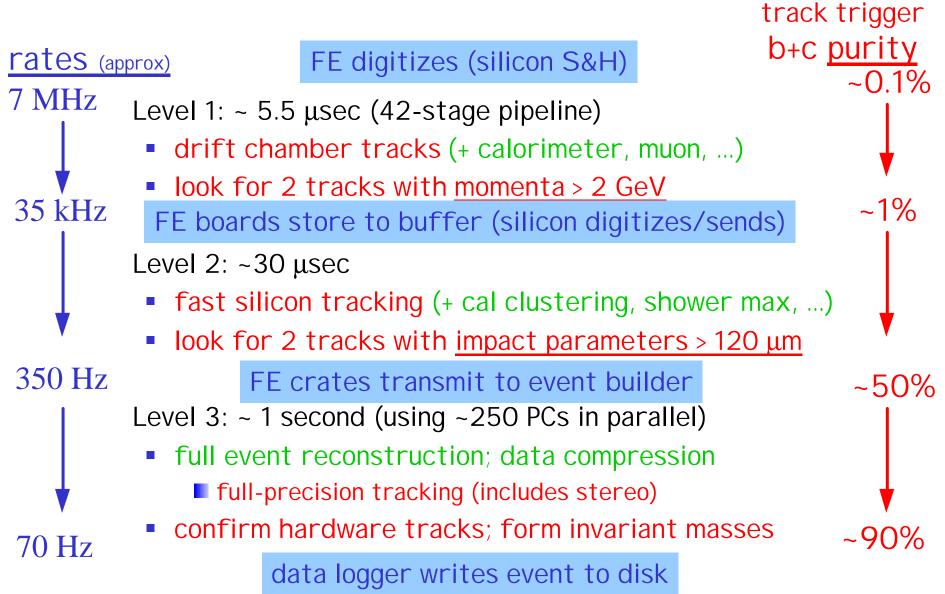

# CDF three-level trigger

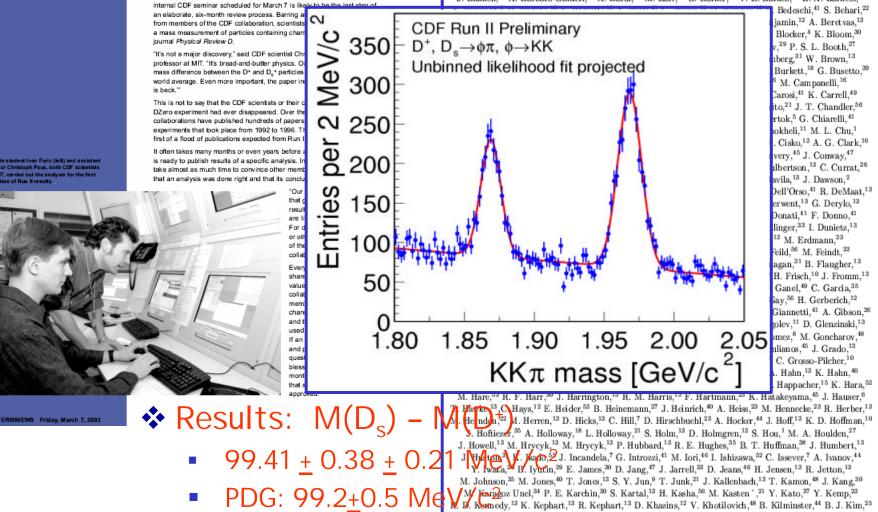

#### New triggers $\rightarrow$ a paper from first 12pb<sup>-1</sup>

#### **CDF approves** first Run II paper

by Kurt Riesselmann

Scientists at CDF have announced that they will soon release the first publication based on data obtained from Fermilah's Collider Bun II. An

#### Measurement of the Mass Difference $m(D_*^+) - m(D^+)$ at CDF II

D. Acosta,<sup>14</sup> T. Affolder,<sup>7</sup> M. H. Ahn,<sup>25</sup> T. Akimoto,<sup>52</sup> M. G. Albrow,<sup>13</sup> B. Alcorn,<sup>13</sup> C. Alexander,<sup>40</sup>

D. Allen,<sup>13</sup> D. Allspach,<sup>13</sup> P. Amaral,<sup>10</sup> D. Ambrose,<sup>40</sup> S. R. Amendolia,<sup>41</sup> D. Amidei,<sup>30</sup> J. Amundson,<sup>13</sup>

A. Anastassov,<sup>47</sup> J. Anderson,<sup>13</sup> K. Anikeev,<sup>29</sup> A. Annovi,<sup>41</sup> J. Antos,<sup>1</sup> M. Aoki,<sup>52</sup> G. Apollinari,<sup>13</sup>

J.-F. Arguin,<sup>50</sup> T. Arisawa,<sup>54</sup> A. Artikov,<sup>11</sup> T. Asakawa,<sup>52</sup> W. Ashmanskas,<sup>10</sup> A. Attal,<sup>6</sup> C. Avanzini,<sup>41</sup>

F. Azfar,<sup>38</sup> P. Azzi-Bacchetta,<sup>39</sup> M. Babik,<sup>13</sup> N. Bacchetta,<sup>39</sup> H. Bachacou,<sup>26</sup> W. Badgett,<sup>13</sup> S. Bailey,<sup>18</sup>

J. Bakken,<sup>13</sup> A. Barbaro-Galtieri,<sup>26</sup> A. Bardi,<sup>41</sup> M. Bari,<sup>51</sup> G. Barker,<sup>23</sup> V. E. Barnes,<sup>43</sup> B. A. Barnett,<sup>22</sup>

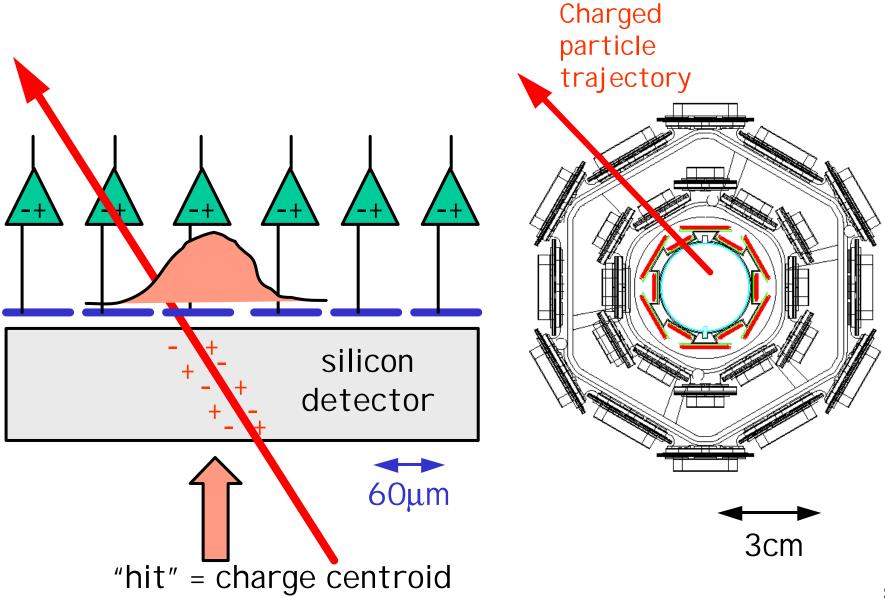

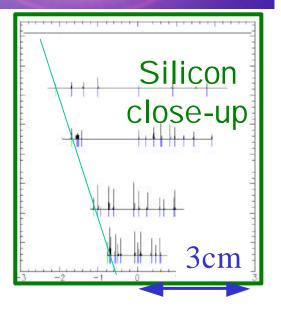

#### Position measurement ("hit") for charged particle

8

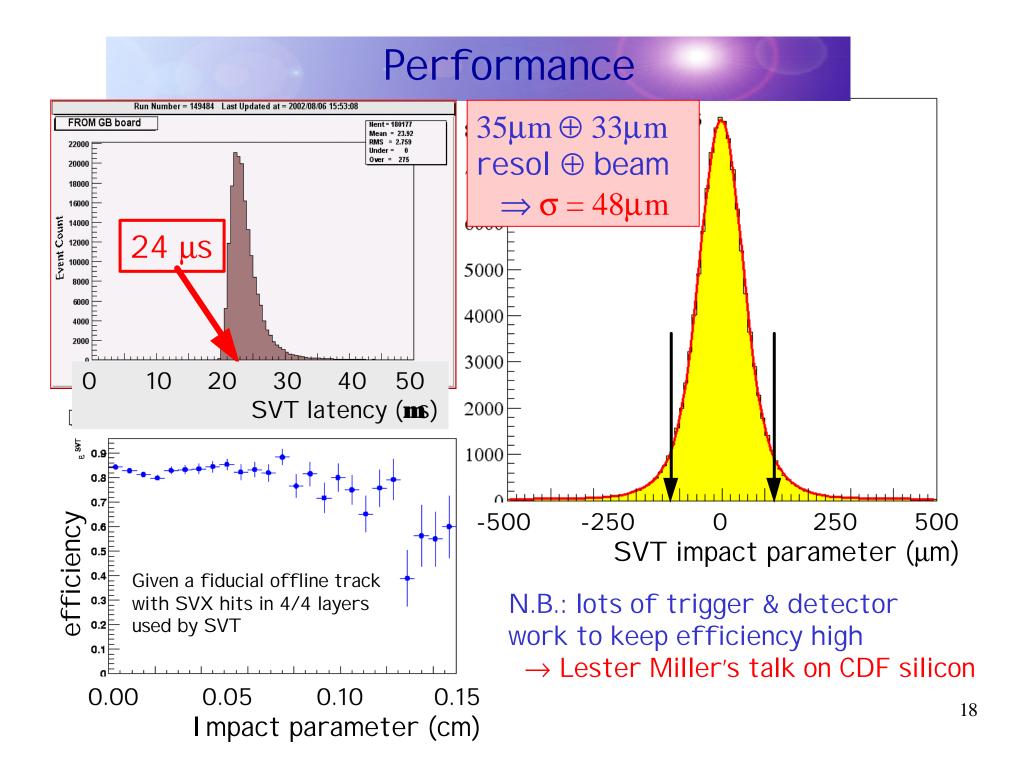

#### Silicon trigger problem synopsis

I nput (every Level 1 accept): outer drift chamber trajectories silicon pulse height for each channel

Output (about 20 microseconds later): trajectories that use silicon points impact parameter:  $\sigma(d)=35um$

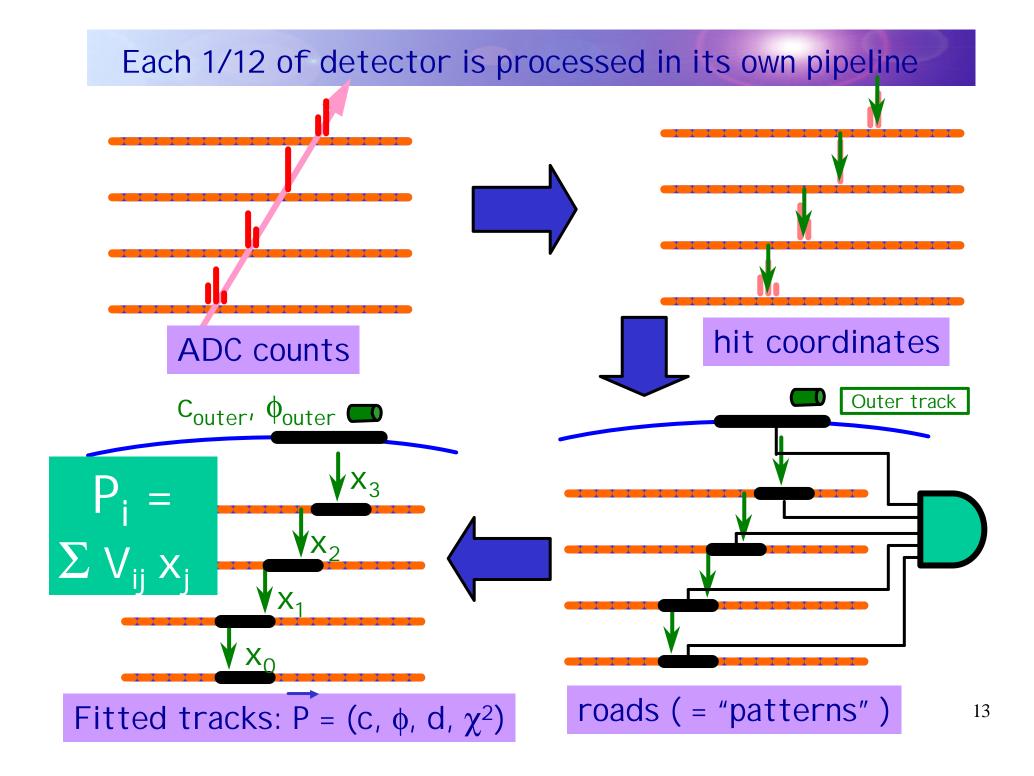

# Doing silicon tracking quickly

Three key features of SVT allow us to do in tens of microseconds what typically takes software hundreds of milliseconds:

- Parallel/pipelined architecture

- Custom VLSI pattern recognition

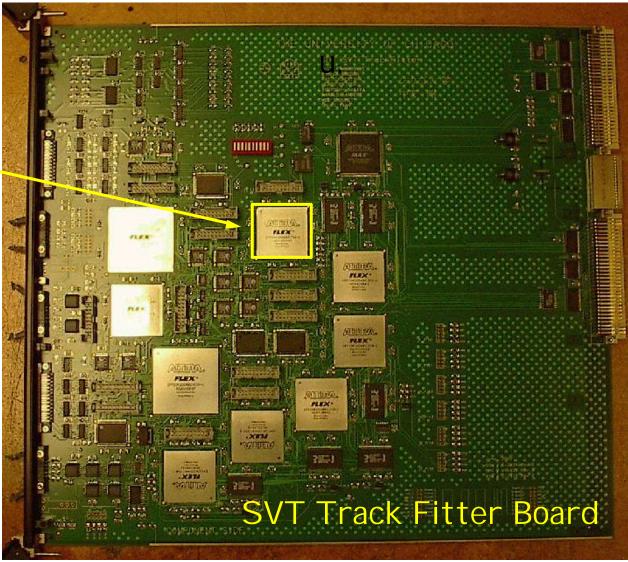

- Linear track fit in fast FPGAs

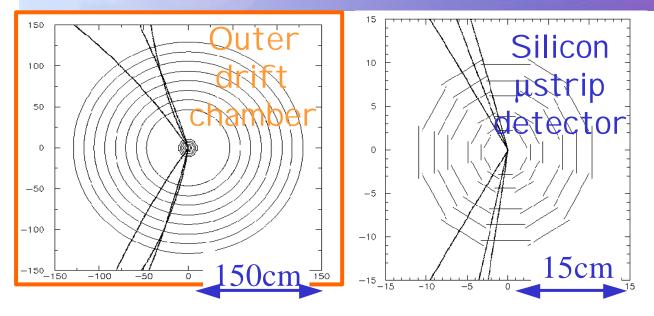

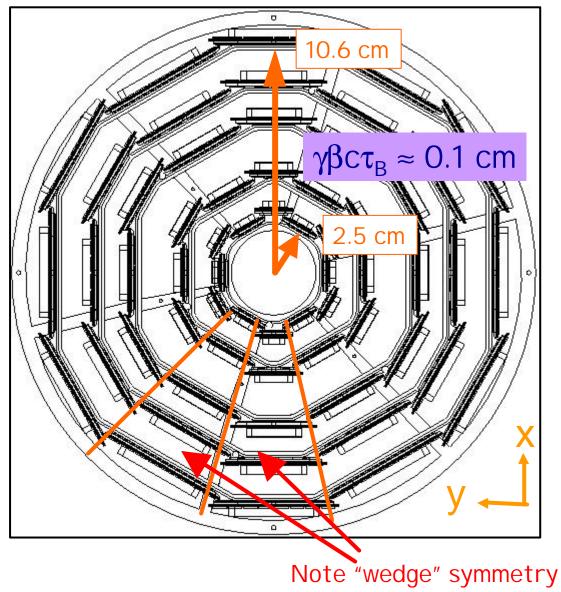

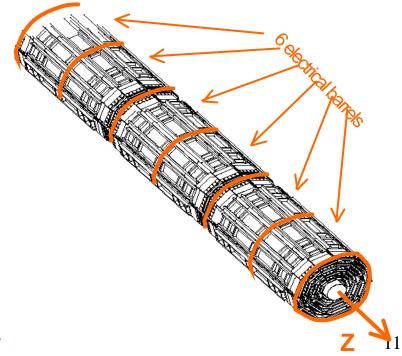

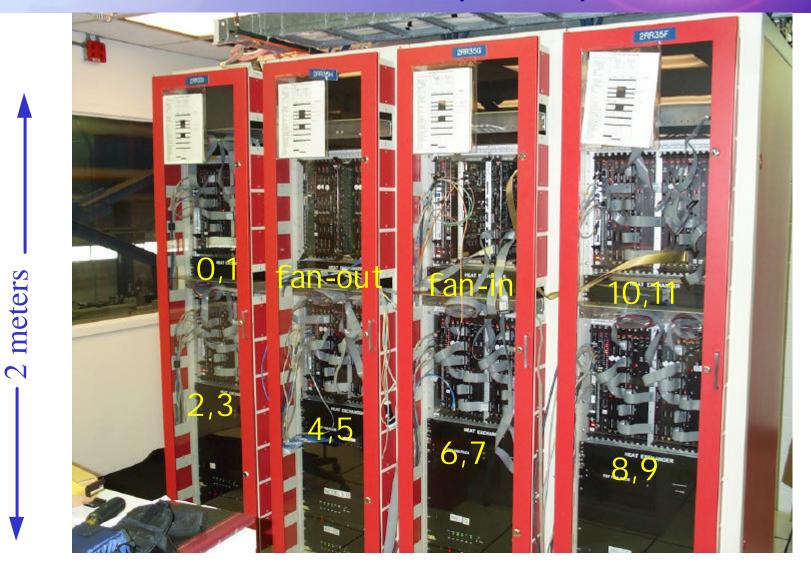

#### Trick #1: symmetry allows parallelism

Symmetric, modular geometry of silicon vertex detector lends itself to parallel processing

#### SVT data volume requires parallelism

Reduces gigabytes/second to megabytes/second Peak (avg): 20 (0.5) GB/s → 100 (1.5) MB/s

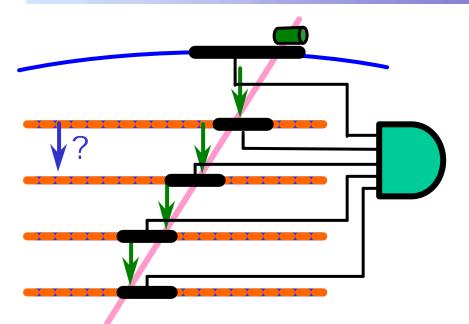

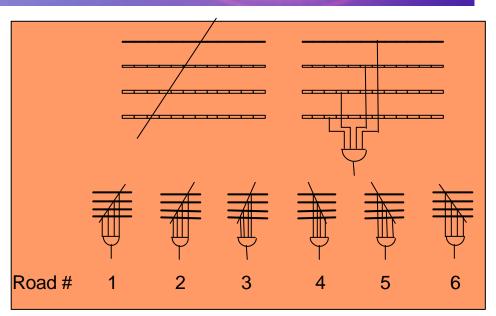

#### 2nd trick: streamlined track finding

The way we find tracks is a cross between

- searching predefined roads

- playing BI NGO

Time ~  $A^*N_{hits} + B^*N_{matchedroads}$

| В  | I  | Ν    | G  | 0  |

|----|----|------|----|----|

| 2  | 17 | 35   | 48 | 61 |

| 10 | 21 | 39   | 53 | 66 |

| 14 | 20 | free | 55 | 65 |

| 8  | 25 | 41   | 52 | 62 |

| 6  | 16 | 37   | 46 | 67 |

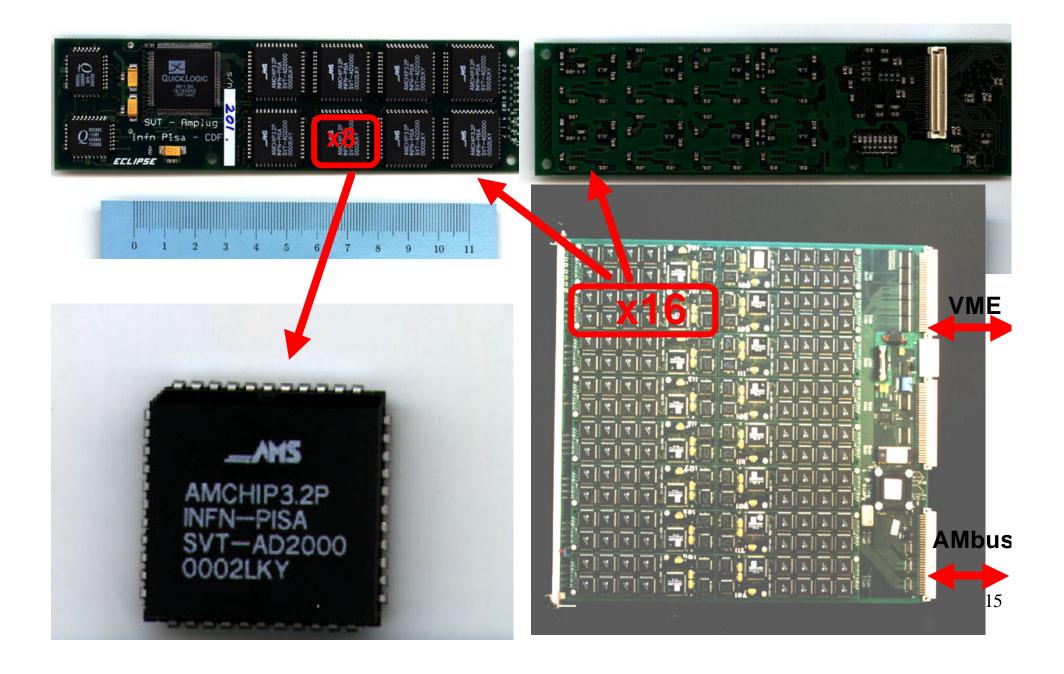

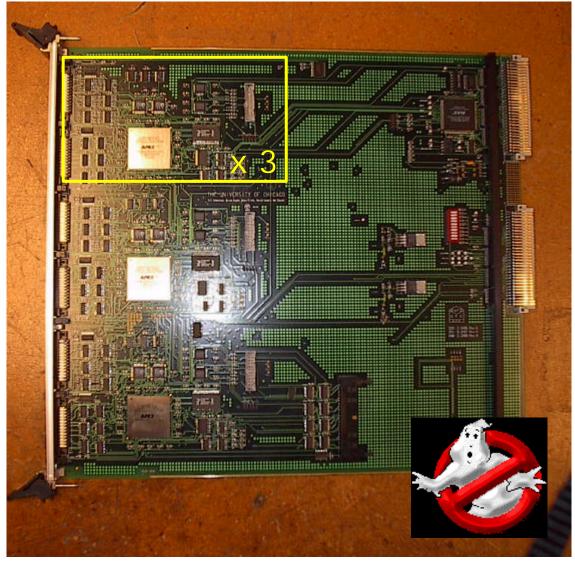

# Custom VLSI AMchip (pattern recognition)

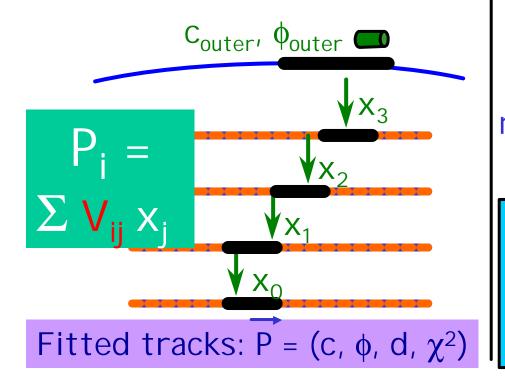

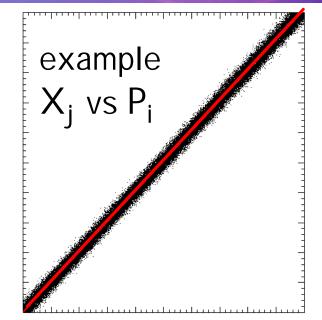

#### Trick #3: linear fit

Circle( $\vec{P}$ ) **Ç** Planes at points  $\vec{X}$  $\vec{X}$  not in general linear in  $\vec{P}$

But for P > 2 GeV, d < 1 mm, linear fit biases d ~ few % ⇒ no problem for trigger

We derive  $V_{ij}\xspace$  by linear regression to Monte Carlo data

<u>Trick #3a</u>: use road as a hint precompute  $V_{ij} X_j^{road}$  $\Rightarrow 250$  nsec per fit !

#### Least squares fit is performed in FPGA

The 6 scalar products are computed in parallel

Each fit done in 250nsec

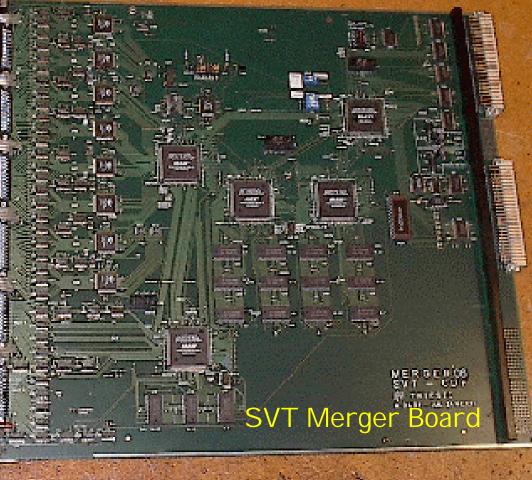

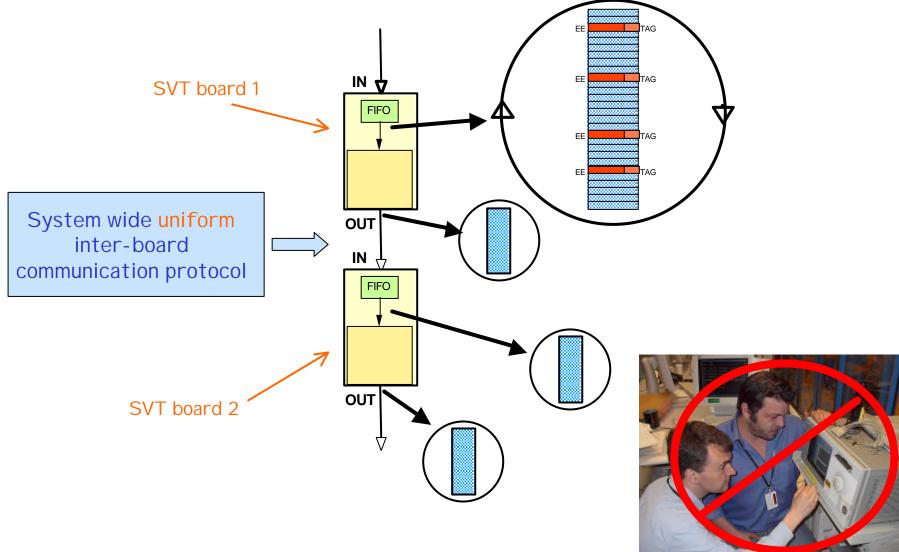

#### Merger & cable capture essence of SVT architecture

Universal cable/format for all SVT data (hits, roads, tracks, ...)

Mergers fan in/out like NLM logic components

Data fan-in done inside FPGAs, not on backplanes

Easy to insert a processing stage, switch source on/off, split off a duplicate copy The board to move the data around was prototyped and tested before other boards were built

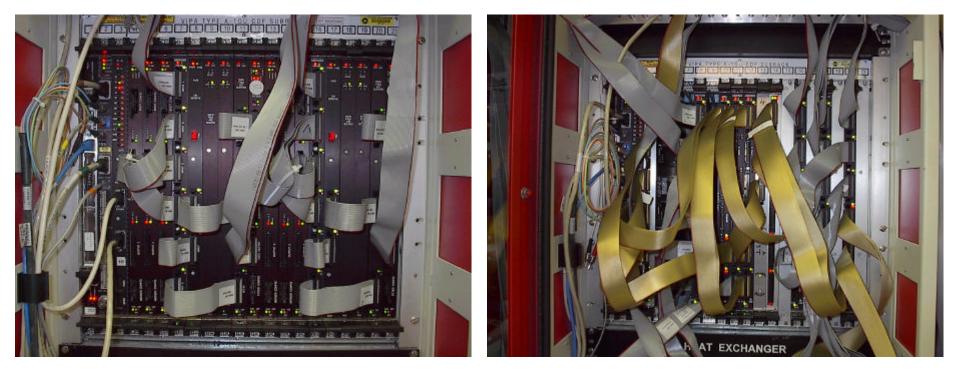

# Most of SVT's cabling was carefully planned a priori

But the flexibility to adapt to the unforeseen was a big plus during commissioning

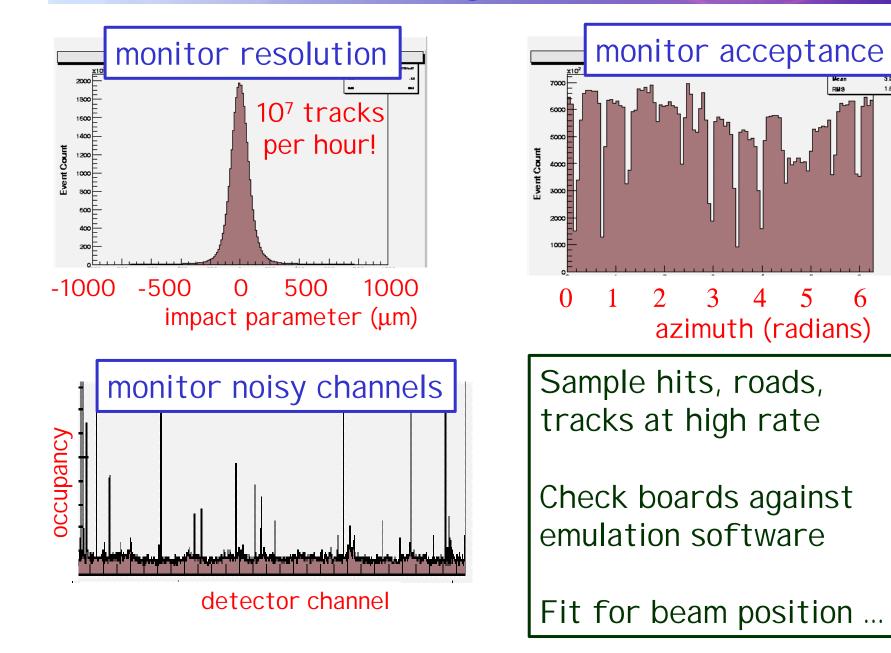

# Circular buffers monitor every data link: like a built-in logic analyzer

# **On-crate monitoring of circular buffers**

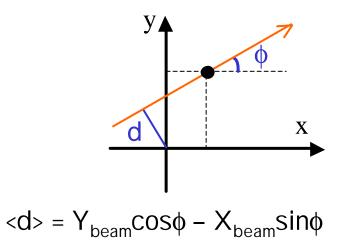

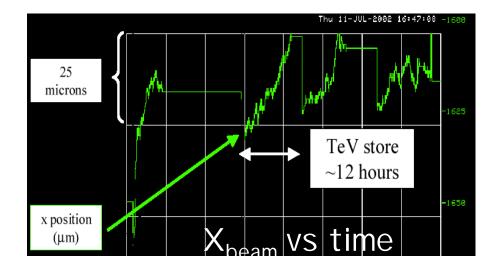

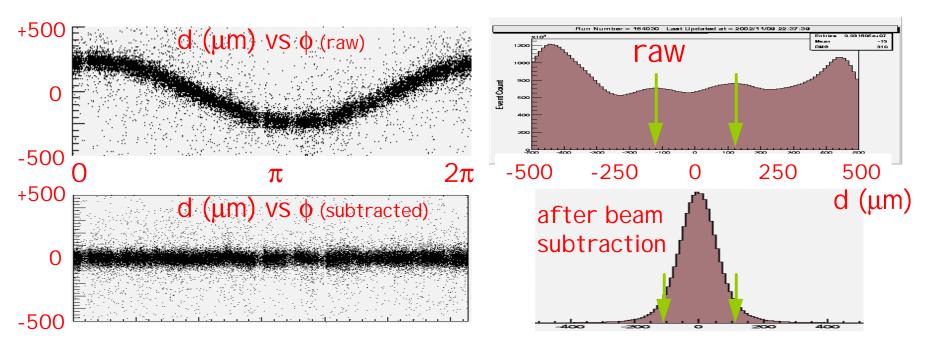

#### Online beamline fit / correction

### SVT board-on-a-chip

#### Input + output + one Altera APEX FPGA

Modern FPGAs have impressive capabilities

#### Swiss army knife:

- Subtract beam offset

- Filter duplicate ("ghost") tracks

- Read diagnostic data into DAQ

- Measure timing

# Why SVT succeeded

- Performance:

- Parallel/pipelined architecture

- Custom VLSI pattern recognition

- Linear track fit in fast FPGAs

#### • Reliability:

Easy to sink/source test data (many boards can self-test)

Modular design; universal, well-tested data link & fan-in/out

- Extensive on-crate monitoring during beam running

- Detailed CAD simulation before prototyping

- See poster by Mircea Bogdan

#### • Flexibility:

System can operate with some (or all) inputs disabled

Building-block design: can add/replace processing steps

Modern FPGAs permit unforeseen algorithm changes

Key: design system for easy testing/commissioning