## UNIVERSITÀ DEGLI STUDI DI PISA INGEGNERIA AEROSPAZIALE: CORSO DI FISICA GENERALE II E ELETTRONICA Prova n. 6 - 27/05/2017

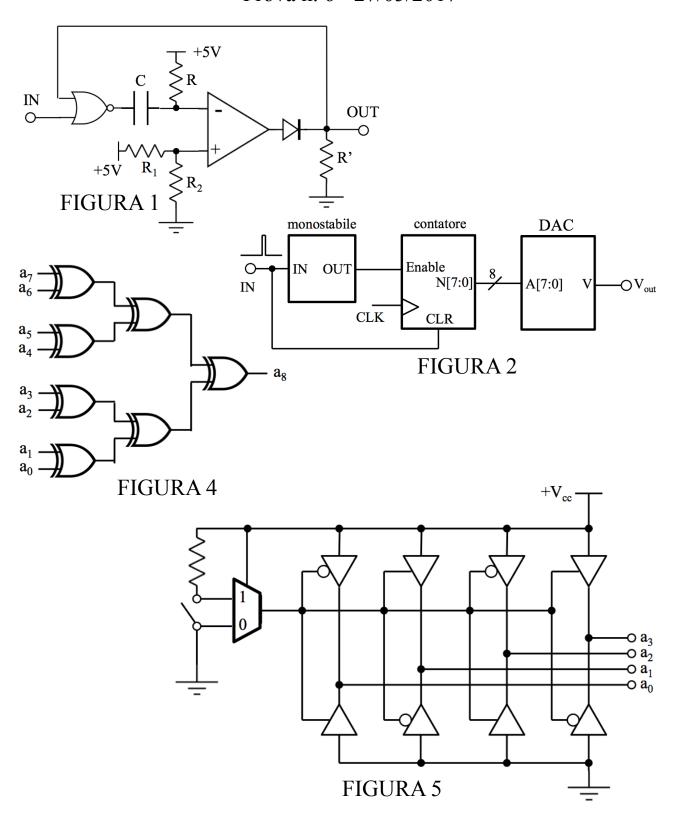

| 1) Il circuito di figura mostra lo schema di un multivibratore monostabile, con stato stabile corrispondente allo 0 in logica TTL, in cui $R_1 = R_2$ , $R = 1.01 \ k\Omega$ , $C = 6.41 \ nF$ . L' amplificatore operazionale è ideale con tensioni di saturazione pari a $V_{cc} = \pm 5 \ V$ . Anche il diodo è da considerarsi tale. Si assuma che anche la porta NOR abbia, in analogia all' operazionale, impedenza infinita in ingresso e nulla in uscita. Si calcoli la durata in $\mu$ s dello stato metastabile (1) indotto da una transizione basso-alto dell' ingresso IN (la cui durata sia trascurabile).                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $A \begin{bmatrix} 0 \end{bmatrix}  B \begin{bmatrix} 2.69 \end{bmatrix}  C \begin{bmatrix} 4.49 \end{bmatrix}  D \begin{bmatrix} 6.29 \end{bmatrix}  E \begin{bmatrix} 8.09 \end{bmatrix}  F \begin{bmatrix} 9.89 \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2) Disponendo di un voltmetro, si può ottenere una stima della durata dello stato metastabile (di cui a precedente esercizio) dalla misura dell' uscita di un convertitore lineare tempo-tensione secondo lo schema mostrato in figura. L' uscita del multivibratore abilita un contatore sincrono ad 8-bit (con reset asincrono sull' ingresso del monostabile), al cui ingresso sia inviato un segnale di CLK di frequenza $f = 2.74$ MHz. Le linee di uscita del contatore pilotano l' ingresso di un DAC ad 8-bit con range dinamico compreso tra 0 ed 1 V. Si calcoli $V_{out}$ in mV allorché il multivibratore sia tornato allo stato stabile.                                 |

| $A \begin{bmatrix} 0 \end{bmatrix}  B \begin{bmatrix} 10.9 \end{bmatrix}  C \begin{bmatrix} 28.9 \end{bmatrix}  D \begin{bmatrix} 46.9 \end{bmatrix}  E \begin{bmatrix} 64.9 \end{bmatrix}  F \begin{bmatrix} 82.9 \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3) Si calcoli in rappresentazione decimale il numero intero più vicino alla media dei numeri interi positivi la cui rappresentazione binaria (a 10-bit) sia $A_0=(1011011010)_2$ , $A_1=(0110100011)_2$ , $A_2=(1001101111)_2$ ed $A_3=(1010000011)_2$ .  A $\boxed{0}$ B $\boxed{244}$ C $\boxed{424}$ D $\boxed{604}$ E $\boxed{784}$ F $\boxed{964}$                                                                                                                                                                                                                                                                                                                               |

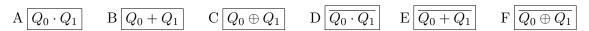

| 4) Per verificare la corretta trasmissione/memorizzazione dati, un trasmettitore utilizza comunemente ur codice di controllo in cui, al bus di N-bit $[a_{N-1},,a_0]$ in trasmissione (con $N=2^n,\ n\in\mathbb{N}$ ), si aggiunge ur ulteriore bit $a_N$ (detto bit di parità) calcolato sulla base della logica combinatoria mostrata in figura (ne caso $N=8$ ). Si dica quale delle seguenti affermazioni sul bus $[a_N,,a_0]$ è corretta: A) nessuna della seguenti; B) $a_N$ è sempre uguale a 0; C) $a_N$ è sempre uguale ad 1; D) il numero di bit uguali ad 1 è sempre dispari; E) il numero di bit uguali ad 1 è sempre pari; F) il numero di bit uguali a 0 è sempre pari. |

| A B C B F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

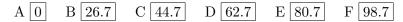

| 5) Si scriva in rappresentazione esadecimale l'uscita del circuito mostrato in figura con l'interruttore aperto (sia barrata la casella vuota accanto alla risposta).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6) Il circuito mostrato in figura è dotato di tre terminali in ingresso (IN0, IN1, IN2) e due di uscita (OUT |

|--------------------------------------------------------------------------------------------------------------|

| ed OUT. Si assuma che l'ingresso IN2 abbia durata minore rispetto al tempo di propagazione di ciascuna       |

| porta logica utilizzata. In base alla sua tabella di verità, si determini di quale dispositivo si tratti:    |

| A) nessuna dei seguenti;                                                                                     |

| B) un flip-flop SR;                                                                                          |

| C) un flip-flop JK;                                                                                          |

| D) un flip-flop D;                                                                                           |

| E) un flip-flop T;                                                                                           |

| F) un contatore.                                                                                             |

| A B C D E F                                                                                                  |

7) Determinare la porta logica identificata da un punto interrogativo nello schema mostrato in figura, perché il circuito realizzi un contatore sincrono a 2-bit (il più significativo dei quali sia  $Q_1$ ).

8) Si modifichi la risposta al precedente esercizio nel caso di un contatore a rovescio.

$$\mathbf{A} \begin{bmatrix} Q_0 \cdot Q_1 \end{bmatrix} \quad \mathbf{B} \begin{bmatrix} Q_0 + Q_1 \end{bmatrix} \quad \mathbf{C} \begin{bmatrix} Q_0 \oplus Q_1 \end{bmatrix} \quad \mathbf{D} \begin{bmatrix} \overline{Q_0 \cdot Q_1} \end{bmatrix} \quad \mathbf{E} \begin{bmatrix} \overline{Q_0 + Q_1} \end{bmatrix} \quad \mathbf{F} \begin{bmatrix} \overline{Q_0 \oplus Q_1} \end{bmatrix}$$

9) In relazione agli esercizi 7 ed 8, si calcoli in MHz la frequenza massima di  $Q_1$  nel caso in cui i flip-flop abbiano tempi di setup  $t_{su} = 1.46$  ns e di ritardo uscita-clock pari a  $t_{co} = 1.57$  ns e la porta logica richieda un tempo di propagazione  $t_{comb} \leq 0.957$  ns.

10) Nel circuito di figura, in una RAM di dimensione 32x10 bits viene registrato lo stato delle linee di uscita di 10 multiplexer a due ingressi il cui bit di controllo è il risultato di un comparatore digitale (N > 1). Gli ingressi dei multiplexer non connessi sono riconosciuti come zeri. Il Write Enable della RAM, non mostrato in figura, è sempre asserito. Un segnale di Clock (CLK) di opportuna frequenza è distribuito con connessione sincrona agli ingressi del contatore, della memoria nonché del registro (a 10-bit) in uscita. Si calcoli in rappresentazione decimale l' uscita del circuito all' occorrenza del sedicesimo impulso di CLK successivo all' ultimo reset del contatore.

A 0 B 197 C 377 D 557 E 737 F 917

Testo n. 0

## FISICA GENERALE II ED ELETTRONICA Prova n. 6 - 27/05/2017